随着各方兴趣的增加,IPC 觉得有必要帮助其他公司开发各种能够确保BGA在制造和测试期间不受损伤的测试方法。这项工作由 IPC 6-10d SMT 附件可靠性测试方法工作小组和 JEDEC JC-14.1 封装设备可靠性测试方法子委员会携手开展,该工作已经完成。 该测试方法规定了以圆形阵列排布的八个接触点。在印刷电路板中心位置装有一 BGA 的 PCA 是这样安放的:部件面朝下装到支撑引脚上,且负载施加于 BGA 的背面。根据 IPC/JEDEC-9704 的建议计量器布局将应变计安放在与该部件相邻的位置。

对于制造过程和组装过程,特别是对于无铅 PCA 而言,其面临的挑战之一就是无法直接测量焊点上的应力。为广泛采用的用来描述互联部件风险的度量标准是毗邻该部件的印刷电路板张力,这在 IPC/JEDEC-9704 《印制线路板应变测试指南》中有叙述。 PCA 会被弯曲到有关的张力水平,且通过故障分析可以确定,挠曲到这些张力水平所引致的损伤程度。通过迭代方法可以确定没有产生损伤的张力水平,这就是张力限值。

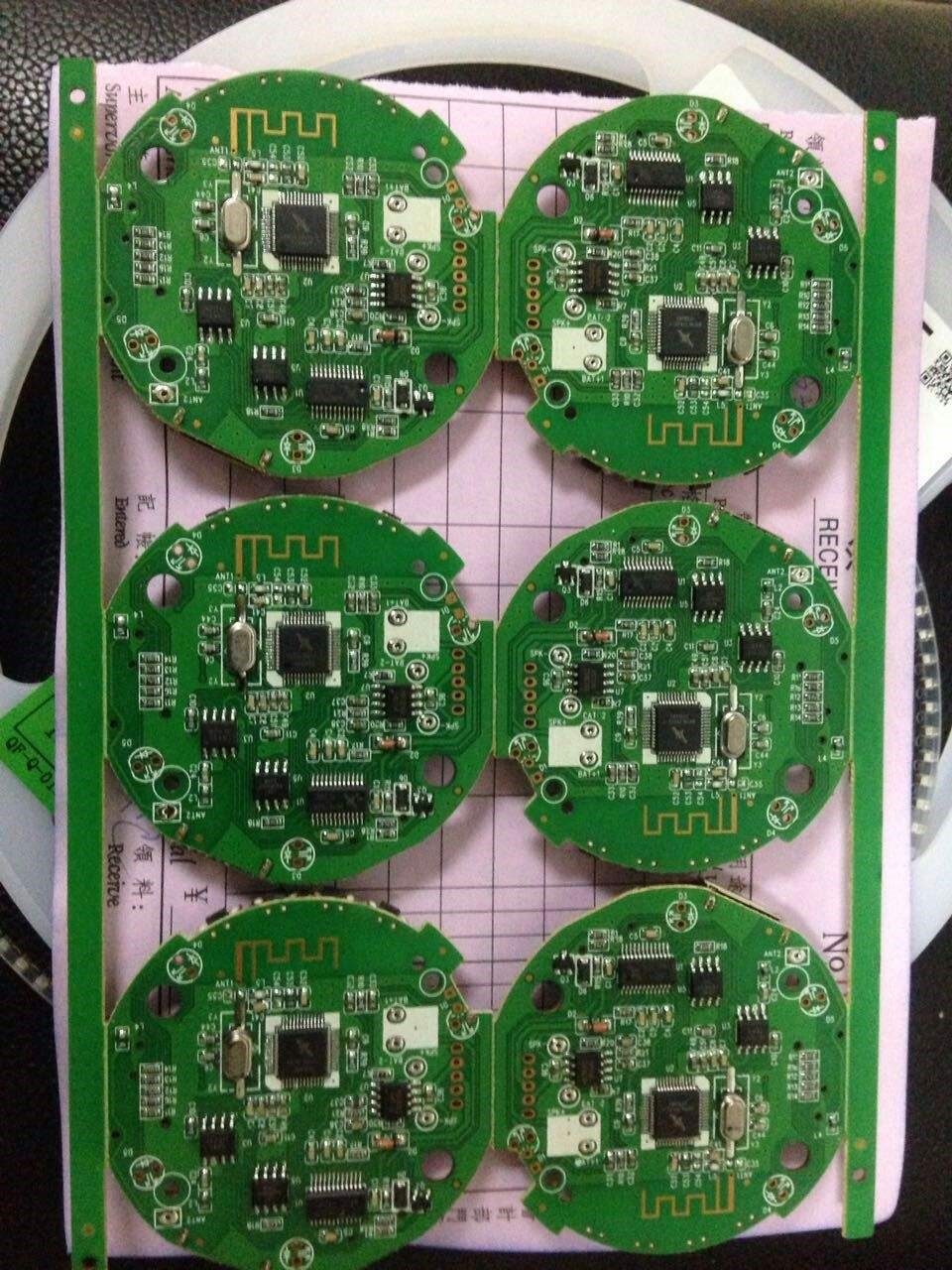

此类薄膜线路一般是用银浆在PET上印刷线路。在此类薄膜线路上粘贴黏贴电子元器件有两种工艺工法,一种谓之传统工艺工法即3胶法(红胶、银胶、包封胶)或2胶法(银胶、包封胶),另一种谓之新工艺即1胶法---顾名思义,就是用一种胶即可完成粘贴黏贴电子元器件,而不再用3种胶或2种胶。此新工艺关键是使用一种新型导电胶,完全具有锡膏的导电性能和工艺性能;使用时完全兼容现行的SMT刷锡膏作业法,毋需添加任何设备。

电子产品追求小型化,以前使用的穿孔插件元件已无法缩小。 电子产品功能更完整,所采用的集成电路(IC)已无穿孔元件,特别是大规模、高集成IC,不得不采用表面贴片元件。 产品批量化,生产自动化,厂方要以低成本高产量,出产优质产品以迎合顾客需求及加强市场竞争力 电子元件的发展,集成电路(IC)的开发,半导体材料的多元应用。 电子科技革命势在必行,追逐国际潮流。可以想象,在intel、amd等国际cpu、图像处理器件的生产商的生产工艺精进到20几个纳米的情况下,smt这种表面组装技术和工艺的发展也是不得以而为之的情况。